Dünaamiline muutmälu

| Arvutimälutüübid |

|---|

| Haihtuvad ehk hävimälud |

| Muutmälu (RAM) |

| Kavandatavad, väljatöötamisel |

| Mittehaihtuvad ehk säilmälud |

| Püsimälu (ROM) |

| Ajaloolised |

Dünaamiline muutmälu ehk DRAM (ingl dynamic random access memory) on muutmälu tüüp, mis säilitab bitiväärtusi kondensaatoris elektrilaenguna või selle puudumisena.

Andmeüksuse lugemiseks ja kirjutamiseks avab juurdepääsu väljatransistor vastavalt juhtsignaalidele. Kuna kondensaatori laeng hakkab lekkevoolu tõttu kiiresti vähenema, siis tuleb laengut toitepinge impulssidega perioodiliselt (vähemalt sadu kordi sekundis) regenereerida ehk värskendada.

Arvuti põhimäluna ehk operatiivmäluna kasutatakse sünkroonset muutmälu (SDRAM), milles värskendamine on sünkroonitud protsessori taktsagedusega.

Mäluelement

[muuda | muuda lähteteksti]

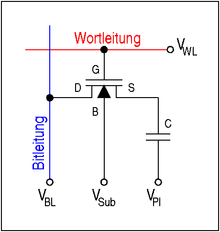

DRAMi mäluelement koosneb ühest transistorist ja kondensaatorist (erinevalt kuuest transistorist staatilises muutmälus). Niisugused elemendid võtavad integraallülituse kiibil vähe ruumi ja tarbivad ka vähe voolu. Seetõttu saab neid kiibile paigutada väga tihedalt ja suurel arvul. Siiski võtab kondensaatori laadimine teatud aja, mistõttu pöördusaeg on suurem kui staatilisel muutmälul (millel piisab ainult trigeri ümberlülitamisest).

Väljatransistor töötab elemendi info lugemisel ja kirjutamisel lülitina. Kui sõnaliinilt (punane) saabub n-MOS-transistori paisule G positiivne pinge, siis muutub neelu D ja lätte S vaheline kanal juhtivaks ja transistor ühendab kondensaatori C bitiliiniga (sinine).

Bitirida ja bitiväli

[muuda | muuda lähteteksti]

Sõnaliinile üksteise kõrvale ühendatud mäluelemendid moodustavad bitirea (ingl page). Elementide arv reas võib olla 210 = 1024 või 2, 4, 8,… korda suurem. Kui sõnaliinile antakse pinge, lülitavad transistorid kõigi elementide sisu (bitid) korraga bitiliinile.

Üksteisele järgnevates ridades on mäluelemendid paigutatud nii, et moodustavad maatriksi, s.t elementide ridade ja veergude kaupa korrastatud bitivälja. Sellel väljal ühendavad sõnajuhtmed ridade kaupa lülitustransistoride tüürelektroodid (paisud) ja bitijuhtmed ühendavad veergude kaupa omavahel transistoride neelud.

Maatriksi alumises servas on bitijuhtmed ühendatud kirjutus-lugemisvõimendiga (ingl sense amplifier), mille toitepinge on võrdne bitijuhtmetele rakendatud pingega. Võimendi on koostatud nii, et lisaks väljaloetud bitisignaalide võimendamisele toimib ta ka lihtsa staatilise mäluna (ingl latch) ja seega veeruandmete salvestina.

Mälukiibil on suur hulk niisuguseid maatrikseid omavahel seostatud rühmadeks, mille bitijuhtmed on toodud 4, 8, 16 või 32 väljaviigule (ingl pin).

Mäluelementide aadresside dekodeerimine

[muuda | muuda lähteteksti]Ridade aadressid suunatakse n aadressijuhtme kaudu readekoodrisse. See valib tema sisendisse ühendatud 2n sõnajuhtmete hulgast üheainsa välja ja aktiveerib selle, nii et sellele lülitub pinge VWL. Seeläbi aktiveeritud mäluelement annab nüüd oma bitiväärtuse (1 või 0) bitijuhtmesse. Lugemisvõimendi võimendab seda, seejärel salvestab ja kirjutab mäluelementi tagasi.

Veeruaadresside dekodeerimine ja andmete valik väljalugemiseks toimub kahes järgus. Esmalt ühendatakse veeruaadressijuhtmed veerudekoodriga. See valib ja aktiveerib ühe 2m veerujuhtmest. Niimoodi valitakse välja korraga k bitijuhet (vastavalt salvesti laiusele). Teise sammuna ühendatakse need k väljavalitud bitijuhet veeruvaliku plokist k väljuva andmejuhtmega.

Selleks et ära hoida signaalide ülekandumist naaberelementidesse ja nende juhtmetesse, rakendatakse krüptograafilisi võtteid.

Andmete lugemine ja kirjutamine

[muuda | muuda lähteteksti]DRAMi mäluelemendi lähteolekus on pingetase sõnajuhtmel madal (nullilähedane) ja transistor mittejuhtivas seisus. Seetõttu värskendatud laeng elemendi kondensaatoril püsib (kui mitte arvestada soovimatu lekkevoolu mõju). Lugemisvõimendi toitepinge on välja lülitatud.

Mäluelemendi aktiveerimiseks määratakse kõigepealt kindlaks, millises mäluplokis antud rida asub, ja siis antakse väljavalitud sõnajuhtmele positiivne pinge.

Andmete lugemine

[muuda | muuda lähteteksti]Andmete lugemiseks tuleb veerudekoodrist saada veeruaadress, Selleks vastav veeruvaliku juhe (CSL) aktiveeritakse ja see ühendab ühe või mitu bitijuhet lugemisvõimendi väljundis bitiväljast lähtuvate andmejuhtmetega. Väljuvat andmesignaali võimendatakse täiendavalt sekundaarvõimendis. Väljaloetud andmed sisestatakse paralleelselt nihkeregistrisse, sünkroonitakse seal välise taktsagedusega ja antakse võimendatult väljundisse.

Andmete kirjutamine

[muuda | muuda lähteteksti]Andmete kirjutamine toimub peaaegu samaaegselt veeruaadressi sisselugemisega. Veeruaadress saadakse veerudekoodrist ja vastavad veerujuhtmed aktiveeritakse. Selle tulemusena luuakse ühendus andmejuhtme ja bitijuhtme vahel. Samaaegselt saabuvad kirjutatavad andmed veeruvalikuplokki ja suunatakse edasi bitijuhtmetele. Lugemisvõimendid toetavad nüüd bitijuhtmete ja vastavate kondensaatorite ümberlaadimist.

Lugemis- ja kirjutustoimingu järel elemendid inaktiveeritakse. Selleks viiakse pinge sõnajuhtmetel nulli. Nii muutub elemendi transistor mittejuhtivaks ja eraldab kondensaatori bitijuhtmest.

DRAMi kondensaator

[muuda | muuda lähteteksti]ITRS (International Technology Roadmap for Semiconductors, rahvusvaheline pooljuhttehnoloogia tegevuskava) on esitanud DRAMi kondensaatorite parameetrite nõutavad väärtused 2017. aastaks:[1]

- suur mahtuvus mäluelemendi kohta (≥ 25 femtofaradit)

- suur suhteline dielektriline läbitavus (≥ 60)

- väikesed mäluelemendi mõõtmed (≤ 0,0024 µm2)

- võimalikult madal temperatuur valmistamisprotsessis (≤ 650 ˚C)

- väike lekkevoolu tihedus (≤ 107,9 nA/cm2)

- väike kondensaatori dielektrikukihi paksus (≤ 7 nm)

- väike mahtuvuse efektiivpaksus (CET, capacitance effective thickness) (≤ 0,45 nm)